Mit dem Thema Elektromagnetische Verträglichkeit (EMV) hat jeder Produktdesigner täglich zu kämpfen – vor allem, wenn frequenzbestimmende Bauteile wie Quarzoszillatoren verwendet werden. Die in den handelsüblichen Quarzoszillatoren verbauten ICs generieren steile Flanken und erzeugen dabei harmonische Oberwellen. Zwar gibt es Spread-Spectrum-Oszillatoren, die allerdings in vielen Applikationen nicht verwendbar, da zu ungenau, sind. Mit einem Center Spread von zum Beispiel ±0,5% wird die Ausgangsfrequenz in einem Bereich von fout ±0,5% moduliert. Basierend auf einer Frequenz von 33,333 oder 66,666 MHz würde die Frequenzmodulation von ±0,5% einem Frequenzmodulationsbereich von 33,333 MHz ±166,665 kHz oder 66,666 MHz ±333,330 kHz entsprechen – zu viel, für ein genaues Clocking. Meistens sind in diesen Applikationen nur ±50 ppm zulässig, also um den Faktor 100 weniger. Eine Frequenzstabilität von ±50ppm entspricht bei 33,333 MHz einer Toleranz von ±1,66665 kHz bzw. bei 66,666 MHz einer Toleranz von ±3,3333 kHz. Die Entwickler mussten in solchen Fällen bislang versuchen, die EMV durch sehr teure Maßnahmen zu reduzieren. Dies ist nun nicht mehr nötig. Denn basierend auf innovativer IC-Technologie, Next Generation Clocking, bietet die Petermann-Technik aus Landsberg am Lech verschiedenste SMD-Silizium-Clock-Oszillatoren mit einem SoftLevel-Ausgangssignal an. Bei der SoftLevel-Technologie handelt es sich um ein programmierbares Ausgangssignal, bei dem durch die Erhöhung der Rise-(trise) und Fall-Time (tfall) die harmonischen Oberwellen eines LVCOMS-Ausgangssignals deutlich reduziert werden können. Dank der SoftLevel-Technologie ist eine exakte Anpassung des Ausgangssignals an den jeweiligen Kundenbedarf möglich.

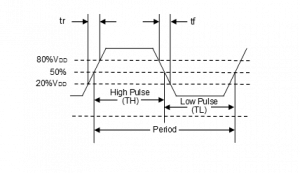

Bild 1: Periodendauer t eines LVCMOS Ausgangssig- nals mit trise und tfall zwischen 20% und 80%.

Was die SoftLevel-Funktion bewirkt

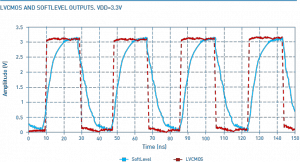

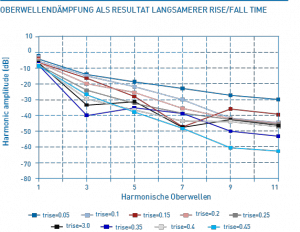

Bild 1 zeigt die Periodendauer t eines LVCMOS Ausgangssignals mit trise und tfall zwischen 20% bis 80%, Bild 2 den Flankenverlauf eines normalen LVCMOS-Rechtecksignals (rote Line) im Vergleich zum SoftLevel-LVCMOS-Ausgangssignals (blaue Line) mit der Versorgungsspannung von +3,3 VDC. Dabei ist deutlich zu sehen, dass die SoftLevel-Funktion die Kanten des Rechtecksignals abrundet (Form ähnlich einer Haifischflosse) und dadurch die harmonischen Oberwellen deutlich reduziert. Bild 3 zeigt die EMV-Dämpfung (ungerade harmonische Oberwellen) in Relation zu der Periodendauer t des Ausgangssignals. trise und tfall werden im Verhältnis zur Periodendauer t des Clocksignals ausgedrückt. Dabei kann trise und tfall im Bereich von 0,05 bis 0,45 (5% bis 45%) von t verlängert werden. Wird trise und tfall im Vergleich zum Basissignal um 5% verlängert, dann kommt die Signalform dem Originalrechtecksignal ziemlich nahe. Mit einer Verlängerung um bis zu 45%, ähnelt die Form des Ausgangssignals immer mehr einer Haifischflosse und die EMV-Dämpfung beträgt bei der 11. harmonischen Oberwelle über –60 dB. Ein enormer Wert, für so eine einfache Anpassung der trise und tfall.

Bild 2: Flankenverlauf eines normalen LVCMOS-Rechtecksignals (rote Line) im Vergleich zu einem SoftLevel-LVCMOS-Ausgangssignal (blaue Line) mit abgerundeten Kanten.

Was kostet den Entwickler die SoftLevel Funktion?

Nichts, denn die SoftLevel Funktion ist ein Standard-Feature von den SMD-Silizium-Clock-Oszillatoren der Serien LPO, LPOP, HTLPO, WTLPO, UPO, HTLPO-AUT und WTLPO-AUT. (AUT = Automotive anhand AEC-Q100). Darüber hinaus sind diese Oszillatorserien in Standardgehäusen mit den Abmessungen von 7 mm x 5 mm, 5 mm x 3,2 mm, 3,2 mm x 2,5 mm, 2,5 mm x 2,0 mm und 2,0 mm x 1,6 mm lieferbar und können damit auf bereits vorhandene Platinenlayouts bestückt werden und damit Quarzoszillatoren sofort direkt ersetzten. Damit das In-House Engineering der PETERMANN-TECHNIK den Kunden optimal beraten und ein Produkt anhand seines Applikationsbedarfes programmieren kann, muss der Entwickler mitteilen, welche trise/tfall Zeit er in seiner Applikation akzeptieren kann. Über die Programmierung – Verlängerung der trise/tfall Zeit – wird die Dämpfung der ungeraden harmonischen Oberwellen dadurch erreicht. Beim Schaltungsdesign für die SMD-Silizium-Clock-Oszillatoren empfehlen die Spezialisten der Petermann-Technik die Verwendung einer Entkoppelungskapazität von 0,1 µF zwischen den Pins Supply Voltage und Ground. Dadurch werden die Einflüsse der eingespeisten Versorgungsspannung deutlich minimiert.

Bild 3: EMV-Reduktion in Relation zu der längeren Periodendauer.

Weitere Vorteile der SMD- Silizium-Clock-Oszillatoren

Die SMD-Silizium-Clock-Oszillatoren der oben genannten Serien sind auch mit einem Versorgungsspannungsbereich von 2,25 bis 3,63 VDC lieferbar. Innerhalb dieses VDD-Bereiches können die Oszillatoren mit jeder x-beliebigen Versorgungsspannung (z.B. 2,5 VDC±10%, 2,8 VDC±10%, 3,0 VDC±10% oder 3,3 VDC ±10%) betrieben werden. Damit muss der Produktentwickler nur noch einen Oszillator für vier klassische Versorgungsspannungen qualifizieren. Dieses Standard-Feature spart dem Entwickler viel Geld in der Bauteilequalifizierung und dem Supply Chain Manager viel Geld in der Beschaffung, Verwaltung und der Lagerung von deutlich weniger Bauteilen. Größere Mengen eines Bauteiles ergeben zudem einen günstigeren Preis. Selbstverständlich ist die beschriebene SoftLevel-Funktion auch für den VVDD-Bereich von 2,25 bis 3,63 VDC als Standard-Feature möglich.

Darüber hinaus verfügen die SMD-Silizium-Clock-Oszillatoren standardmäßig über sehr genaue Frequenztoleranzen, zum Beispiel ±20ppm@–40/85 °C, ±30ppm@–40/105 °C und ±50ppm@–40/125 °C. Selbstverständlich sind auch AEC-Q100-kompatible Oszillatoren (HTLPO-AUT und WTLPO-AUT) mit all den beschriebenen Features lieferbar.

SoftLevel-Funktion verbessert das EMV-Verhalten

Durch einfache und kostenlose Anpassung von trise und tfall des Ausgangssignals kann mit der SoftLevel-Funktion das EMV-Verhalten von SMD-Clock-Oszillatoren deutlich verbessert werden, sodass der Entwickler nicht mehr durch teure Maßnahmen das EMV-Verhalten seiner Applikation verbessern muss. Die SMD-Silizium-Clock-Oszillatoren können sofort auf bestehende Platinenlayouts bestückt werden. Durch den VDD-Bereich von 2,25 bis 3,63 VDC und die sehr engen Standard-Frequenztoleranzen kann zudem sehr viel Geld in der Bauteilequalifizierung, -beschaffung, -verwaltung und der -lagerung eingespart werden.

Weitere Informationen unter:

Silizium Oszillatoren (wie MEMS)

oder

Silizium Oszillatoren Produktübersicht

Technische Fragen:

Telefon: 0 81 91 / 30 53 95

E-Mail: info@petermann-technik.de